# **Моделирование эффекта ослабления паразитного туннелирования электронов в элементах флеш-памяти с глубоким стоком**

**О. Г. Жевняк**

*Белорусский государственный университет, Минск, Беларусь*

*e-mail: [zhevnyakog@mail.ru](mailto:zhevnyakog@mail.ru)*

На основе моделирования методом Монте Карло рассчитаны зависимости величины паразитного туннельного тока электронов вдоль проводящего канала элементов флеш-памяти для МОП-транзисторов с плавающим затвором с разной глубиной залегания стока. Показано, что для глубоких 100 нм стоков по сравнению с мелкими 10 нм стоками отношение этой величины к величине тока стока уменьшается в полтора-два раза. Это обусловлено резким уменьшением концентрации электронов у границы Si/SiO<sub>2</sub>, в транзисторах с глубоким стоком.

**Ключевые слова:** МОП-транзистор; флеш-память; туннелирование электронов; дрейфовый ток.

## **Simulation of suppression of electron parasitic tunneling in flash-memory cells with deep drain**

**O. G. Zhevnyak**

*Belarusian State University, Minsk, Belarus, e-mail: [zhevnyakog@mail.ru](mailto:zhevnyakog@mail.ru)*

By Monte Carlo simulation the dependencies of parasitic electron tunneling current value along the channel in flash-memory cells on basis of short channel MOSFET with floating gate as well as drain with various depth are calculated. It is shown that the value of parasitic tunnel current in transistor with deep drain decreases by 2 times in comparison with one having shallow drain. It is connected with the significant decreasing of electron concentration at the surface region of flash-memory cell for transistors with deep drain.

**Keywords:** MOSFET; flash-memory; electron tunneling; drift current.

### **Введение**

С уменьшением размеров элементов флеш-памяти неизбежно повышается вероятность появления в них паразитных токов недопустимой величины, которые могут привести к искажению хранящихся в них битов информации. В качестве элементов флеш-памяти используется короткоканальный МОП-транзистор с плавающим затвором, и ослабление процесса паразитного туннелирования в них является актуальной задачей для проектирования перспективных конструкций такого рода транзисторов [1, 2].

Паразитное (спонтанное) туннелирование электронов на плавающий затвор транзистора могут осуществлять электроны, находящиеся у поверхности раздела Si/SiO<sub>2</sub> непосредственно у туннельного оксида, при условии достижения ими энергий от 0.2–0.3 эВ и выше [3] (вероятность туннелирования при энергиях меньше 0.2 эВ ничтожно мала – меньше 10<sup>-20</sup>). Чем больше электронов с высокими энергиями находится у туннельного оксида, тем выше паразитный ток. Таким образом, двумя факторами, определяющими паразитное туннелирование, является концентрация электронов  $N_{el}$  у поверхности раздела Si/SiO<sub>2</sub> и их энергия  $E$ .

В настоящей работе была поставлена цель с помощью кинетического моделирования переноса электронов в канале МОП-транзистора с плавающим затвором методом Монте-Карло оценить влияние глубины залегания истоковой и стоковой областей этого транзистора на величину плотности паразитного тока электронов на плавающий затвор и, прежде всего, на величины  $N_{el}$  и  $E$ .

## 1. Описание модели

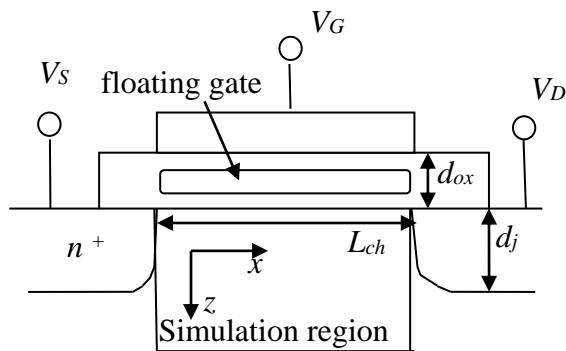

На рис. 1 приведена геометрическая схема конструкции моделируемого элемента флеш-памяти.

*Rис. 1. Конструктивно-технологические параметры моделируемого элемента флеш-памяти:  $L_{ch} = 0.15$  мкм,  $d_{ox} = 7$  нм,  $N_D = 10^{26}$  м $^{-3}$ ,  $N_A = 10^{24}$  м $^{-3}$ ,  $V_G = V_D = 2$  В,  $V_S = 0$  В*

При исследовании влияния глубины залегания истока и стока  $d_j$  на процесс паразитного туннелирования мы должны рассмотреть, как оно влияет на величины  $J_{tun}$ ,  $N_{el}$  и  $E$ .

Алгоритмы моделирования с помощью метода Монте-Карло паразитного туннельного тока для рассматриваемого на рис. 1 транзистора с плавающим затвором описаны в наших работах [3, 4]. Процедуры самосогласованного решения уравнений Пуассона и Больцмана, позволяющие рассчитать изменения по области моделирования величин средней энергии электронов и плотности дрейфового тока, рассмотрены в монографии [5]. Мы моделировали три транзистора с глубиной залегания областей истока и стока  $d_j$ , равными 10 нм (мелкий сток), 50 нм (глубокий сток) и 100 нм (сверхглубокий сток).

## Результаты моделирования и их обсуждение

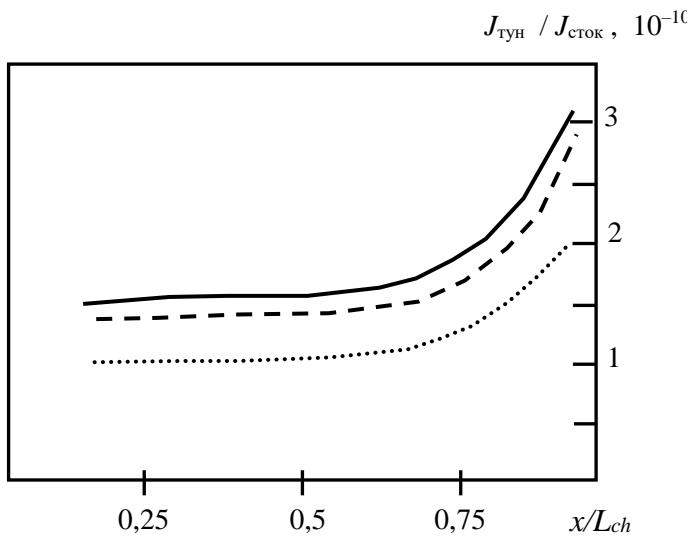

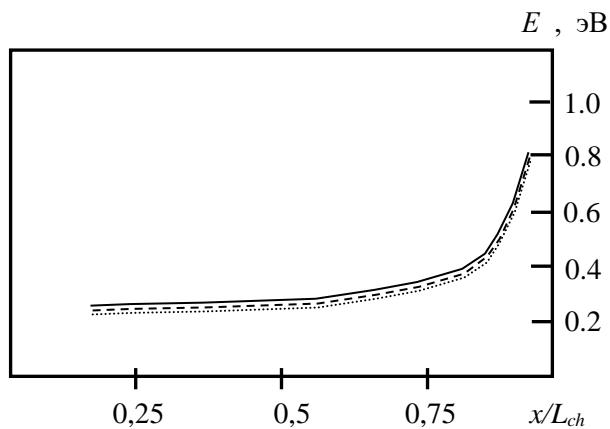

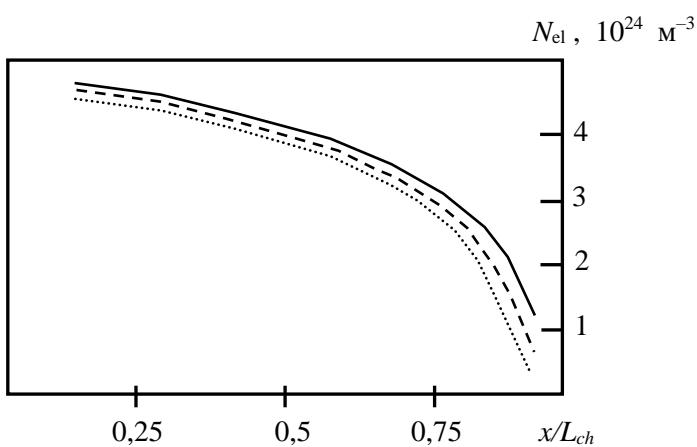

На рис. 2–4 приведены полученные нами в результате моделирования зависимости отношения плотности туннельного тока электронов к плотности дрейфового тока у поверхности Si/SiO<sub>2</sub>, концентрации электронов у этой поверхности и среднего значения энергии электронов вдоль проводящего канала для элементов флеш-памяти с тремя разными значениями глубины залегания истоковой и стоковой областей. На всех представленных ниже рисунках непрерывные кривые соответствуют транзистору с  $d_j = 10$  нм, штриховые –  $d_j = 50$  нм и пунктирные –  $d_j = 100$  нм.

Рис. 2. Отношение плотности туннельного паразитного тока к плотности тока стока вдоль проводящего канала моделируемого элемента флеш-памяти

На рис. 2 приведено изменение вдоль проводящего канала от истока ( $x/L_{ch} = 0$ ) к стоку ( $x/L_{ch} = 1$ ) отношения плотности туннельного тока к дрейфовому у поверхности раздела Si/SiO<sub>2</sub>. Видно, что в транзисторах с глубокими стоками это отношение меньше. Также из рис. 2 следует, что вблизи стока величина  $J_{\text{тун}} / J_{\text{сток}}$  для всех трёх рассматриваемых элементов флеш-памяти увеличивается в два раза по сравнению с областью в начале проводящего канала. Такое поведение легко объясняется ростом энергии электронов в направлении стока, как демонстрируют кривые на рис. 3. Однако, как можно видеть, энергия возрастает приблизительно в три раза, а, учитывая, что вероятность паразитного туннелирования имеет сложную экспоненциальную зависимость от энергии электронов ([3]), на рис. 2 следовало бы ожидать куда более сильного роста относительной величины паразитного туннельного тока в направлении стока. Причина такого невысокого роста объясняется поведением кривых на рис. 4. Одновременно с ростом энергии электронов вдоль канала наблюдается существенное уменьшение количества электронов у поверхности раздела Si/SiO<sub>2</sub>. И, как легко видеть, в транзисторах с глубокими стоками это уменьшение гораздо более значительное – к примеру, у транзистора с  $d_j = 10$  нм концентрация уменьшается в 4 раза, тогда как у транзистора с  $d_j = 100$  нм в 15 раз.

Глубина залегания стока на величину средней энергии также оказывает влияние, но очень незначительное, что следует из рис. 3. Поэтому главным фактором, приводящим к ослаблению паразитного туннелирования в элементах флеш-памяти с глубоким стоком по сравнению с элементами с мелким стоком, является увод электронов с приповерхностных областей транзистора с плавающим затвором в глубь подложки. То есть, в транзисторах с глубоким стоком электроны в значительной мере дрейфуют от истока к стоку не у поверхности Si/SiO<sub>2</sub>, а в некотором удалении от неё, что и приводит к заметному подавлению процесса паразитного туннелирования.

*Рис. 3. Изменение среднего значения энергии вдоль проводящего канала моделируемого элемента флеш-памяти*

*Рис. 4. Изменение значения концентрации электронов у поверхности раздела Si/SiO<sub>2</sub> вдоль проводящего канала моделируемого элемента флеш-памяти*

### Заключение

Таким образом, в настоящей работе путем численного моделирования процесса туннелирования электронов на плавающий затвор элементов флеш-памяти, изучено влияние глубины залегания стока на величину паразитного туннельного тока. Показано, что в МОП-транзисторах с плавающим затвором, являющихся основой этих элементов, в случае глубоких стоков наблюдается заметное уменьшение величины паразитного туннельного тока.

### Библиографические ссылки

1. *De Salvo B. Silicon Non-Volatile Memories: paths of innovation.* London: Wiley-ISTE Ltd. 2009. 256 p.

2. *Kang Y. H. A simple flash memory cell model for transient circuit simulation // IEEE Trans. Electron Device Lett.* 2005. Vol. 26, No. 8. P. 563–565.

3. Жевняк О. Г. Моделирование туннельного тока в элементах флеш-памяти // Международный научно-исследовательский журнал. 2015. Вып. 9., Ч. 3. С. 49–53.

4. Жевняк О. Г. Моделирование влияния глубины залегания стока на паразитные туннельные токи в элементах флеш-памяти / О. Г. Жевняк, В. М. Борзов, А. В. Борзов // Евразийский Союз ученых. Серия: техн. и физ.-мат. науки. 2021. Том. 1, № 12. С. 58–61.

5. Моделирование методом Монте-Карло приборных структур интегральной электроники / В. М. Борзов [и др.], Минск : БГУ. 2007. 175 с.