# ПРОЕКТИРОВАНИЕ УСТРОЙСТВ МОДУЛЯРНОЙ АРИФМЕТИКИ

### Д. А. Городецкий

Из научно-технической литературы известно, что использование систем остаточных классов [1; 2] и модулярных систем счисления [3] позволяет в ряде случаев ускорить процесс обработки информации за счет параллельного процесса выполнения операций с малоразрядными остатками от деления числа на заранее выбранные натуральные основания [1; 2; 3]. Кроме того, модулярные коды позволяют обнаруживать и исправлять ошибки как при хранении и передачи числовой информации, так и при выполнении (вычислении) арифметических операций [1; 2].

Основными функциональными узлами модулярных систем счисления являются сумматоры и умножители P, где P=2n+1 и число n- натуральное. Сумматоры и умножители по модулю P могут использоваться не только в качестве самостоятельных устройств, выполняющих операции сложения или умножения по модулю P, но также служат основой для построения других (более сложных) вычислительных устройств по модулю P.

Проектирование вычислительных устройств модулярной арифметики является весьма сложной задачей, кроме того, проектируя такие устройства необходимо минимизировать такие параметры, как 1) конструктивная сложность (суммарное число входов логических элементов); 2) число уровней; 3) число внешних выводов (суммарное число входов и выходов схемы).

Большинство известных схем вычислительных устройств унитарных кодов по модулю три имеют относительное небольшую конструктивную сложность и небольшое число уровней. В то же время при проектировании подобных устройств уделяется мало внимания на проблему минимизации числа внешних выводов.

В работе предлагаются две логические схемы вычислительных устройств унитарных кодов по модулю три с минимальным числом внешних выводов и одно устройство с управляющим входом.

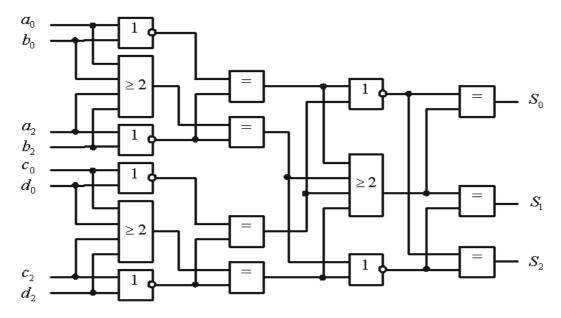

**1. СУММАТОР УНИТАРНЫХ КОДОВ ПО МОДУЛЮ ТРИ**, ориентированный на реализацию операции  $A + B + C + D = S \pmod{3}$ , логическая схема которого приведена на *puc*. 1.

Сумматор унитарных кодов по модулю три работает следующим образом. На входы сумматора поступают разряды «равно нулю» и «равно двум» унитарных кодов первого  $A = (a_0, a_1, a_2)$ , второго  $B = (b_0, b_1, b_2)$ , третьего  $C = (c_0, c_1, c_2)$  и четвертого  $D = (d_0, d_1, d_2)$  операндов, где

Рис. 1. Сумматор унитарных кодов по модулю три

$a_0,b_0,c_0,d_0,a_1,b_1,c_1,d_1,$   $a_2,b_2,c_2,d_2\in\{0,1\}$ . При этом  $a_k=1$  ( $b_k=1,$   $c_k=1,$   $d_k=1$ ) тогда и только тогда, когда  $A=k\pmod 3$  (соответственно, ,  $C=k\pmod 3$  и  $D=k\pmod 3$ ), где k=0,1,2. На выходах сумматора формируется унитарный код результата выполнения операции  $A+B+C+D=S\pmod 3$ , где  $S=(s_0,s_1,s_2)$  и  $s_0,s_1,s_2\in\{0,1\}$ . Причем  $s_k=1$  тогда и только тогда, когда  $A+B+C+D=k\pmod 3$  и k=0,1,2.

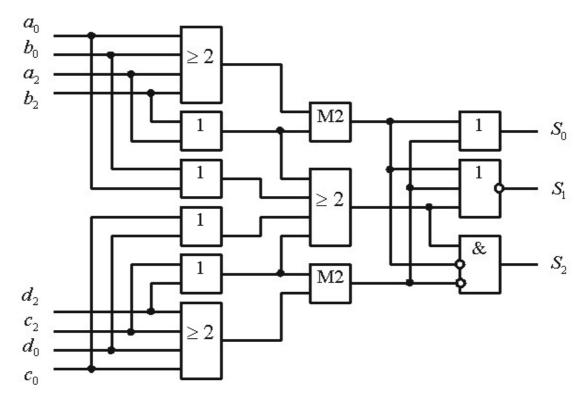

**2. ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО УНИТАРНЫХ КОДОВ ПО МО- ДУЛЮ ТРИ**, предназначенно для реализации операции  $(A+B)*(C+D)=S \pmod{3}$ . Логическая схема устройства приведена на *puc*. 2.

Вычислительное устройство работает по аналогии с сумматором унитарных кодов по модулю три, описанным выше, за тем лишь отличием, что на выходах устройства формируется унитарный двоичный код результата выполнения операции  $(A+B)*(C+D)=S \pmod 3$ , где  $S=(s_0,s_1,s_2)$  и  $s_0,s_1,s_2\in\{0,1\}$ . Причем  $s_k=1$  тогда и только тогда, когда  $(A+B)*(C+D)=k \pmod 3$  и k=0,1,2.

Основным достоинством вышеприведенных вычислительных устройств унитарных кодов по модулю три является минимальное число внешних выводов.

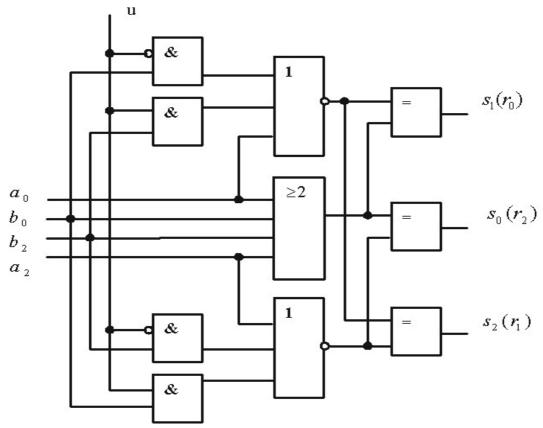

**3. ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО УНИТАРНЫХ КОДОВ ПО МО- ДУЛЮ ТРИ С УПРАВЛЯЮЩИМ ВХОДОМ**, предназначенно для выполнения операций  $A + B = S \pmod{3}$  или  $A - B = R \pmod{3}$ . Логическая схема устройства приведена на *puc*. 3.

Рис. 2. Вычислительное устройство унитарных кодов по модулю три

Вычислительное устройство унитарных кодов по модулю три работает следующим образом. На информационные входы устройства поступают значения разрядов «равно нулю» и «равно двум» унитарных кодов первого  $A = (a_0, a_1, a_2)$  и второго  $B = (b_0, b_1, b_2)$  операндов, где  $a_0, b_0, a_1, b_1, a_2, b_2 \in \{0,1\}$ . При этом  $a_k = 1$  ( $b_k = 1$ ) тогда и только тогда, когда  $A = k \pmod 3$  (соответственно,  $B = k \pmod 3$ ), где k = 0,1,2. На управляющий вход устройства поступает управляющий сигнал u = 0 или u = 1. На выходах устройства формируется унитарный двоичный код результата выполнения операции  $A + B = S \pmod 3$ , если u = 0, или операции  $A - B = R \pmod 3$ , если u = 1. Здесь  $S = (s_0, s_1, s_2)$  и  $R = (r_0, r_1, r_2)$ , где  $s_0, r_0, s_1, r_1, s_2, r_2 \in \{0,1\}$ . Причем  $s_k = 1$  ( $r_k = 1$ ) тогда и только тогда, когда  $A + B = k \pmod 3$  (соответственно,  $A - B = k \pmod 3$ ) и k = 0,1,2.

Основным достоинством приведенного вычислительного устройства унитарных кодов по мо дулю три является минимальное число внешних выводов и возможность

Кроме того, названные устройства имеют небольшую конструктивную сложность и небольшую глубину (относительно известных аналогов). Причем, на все три устройства к настоящему времени оформлены заявки на Патент Республики Беларусь.

*Puc. 3* Вычислительное устройство унитарных кодов по модулю три с управляющим входом

#### Литература

- 1. *Торгашев В. А.* Система остаточных классов и надежность ЦВМ. М.: Советское радио, 1973. 120 с.

- 2. Долгов А. И. Диагностика устройств, функционирующих в системе остаточных классов. М.: Радио и связь, 1982. 64 с.

- 3. *Коляда А. А., Пак И. Т.* Модулярные структуры конвейерной обработки информации. Мн.: Университетское, 1992. 256 с.

## УСТОЙЧИВОСТЬ МНОГОКРИТЕРИАЛЬНОЙ ЗАДАЧИ РАЗБИЕНИЯ

#### Е. Е. Гуревский

При решении практических задач оптимизации приходиться учитывать различные факторы неопределенности, такие как неточность входной информации, ошибки округления, погрешность вычислений, неадекватность математических моделей реальным процессам и т.п. Это обуславливает внимание многих специалистов к изучению разнообразных аспектов теории некорректных задач, и в частности, к вопросам устойчи-